Building a complex SoC subsystem using Vivado IDE

We will start from the Electronic Trading System (ETS) SoC hardware design and add more features to it, such as connecting a master interface from within the Programmable Logic (PL) side of the FPGA SoC to the Accelerator Coherency Port (ACP) of the Processing Subsystem (PS) side. We will also make sure that the PS design includes all the hardware features necessary to run an embedded OS such as the timers, the storage devices, the Input/Output (IO) peripherals, and the communication interfaces. Let’s get started:

- Launch the Vivado IDE and open the ETS SoC hardware design we built in Chapter 7, FPGA SoC Hardware Design and Verification Flow.

- Go to IP Integrator and click Open Block Design, causing the block design to open in the Vivado IP Integrator window.

- Double-click on ZYNQ7 Processing System to open it for customization. The following window shall open:

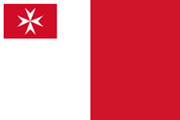

Figure 10.1 – ETS SoC...