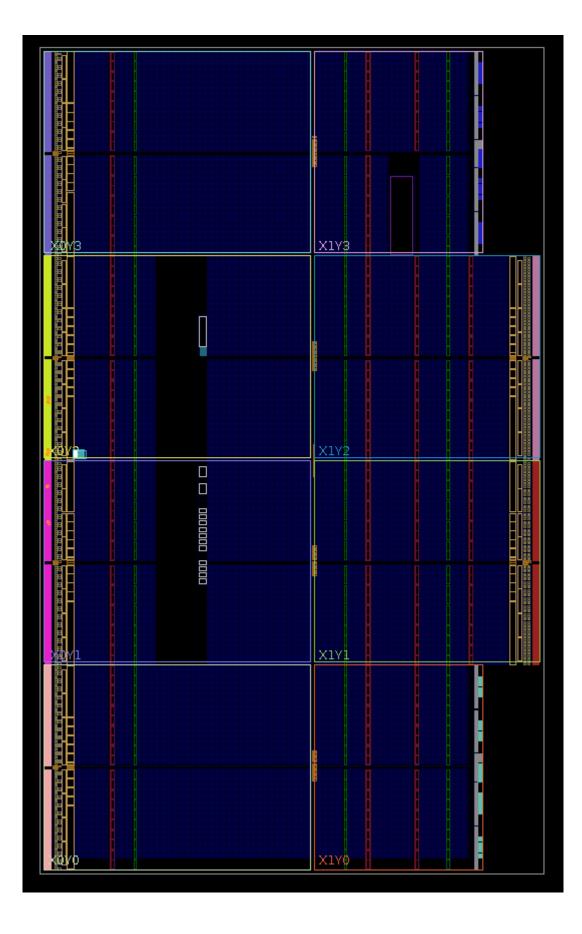

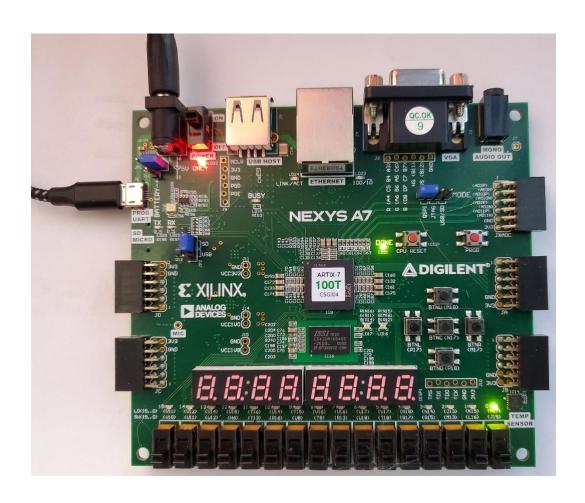

**Chapter 1: Introduction to FPGA Architectures and Xilinx Vivado**

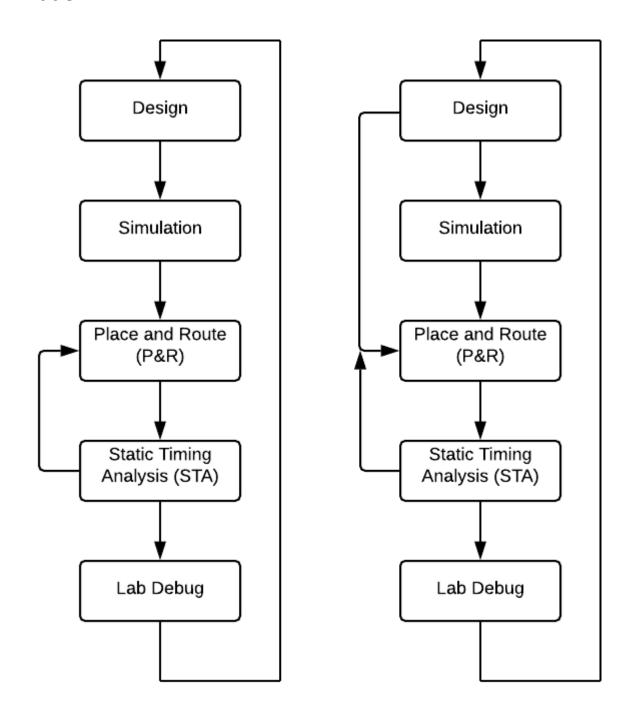

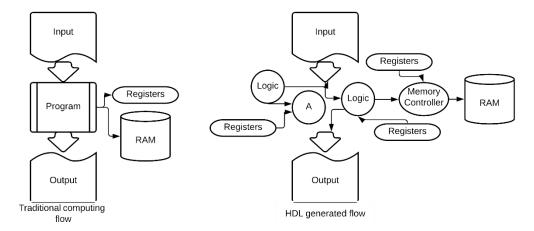

Simple ASIC Flow

Simple FPGA Flow

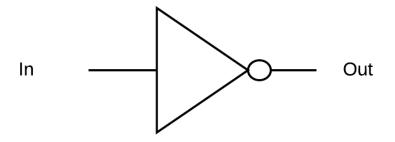

| In | Out |

|----|-----|

| 0  | 1   |

| 1  | 0   |

**Graphical Representation**

Truth Table

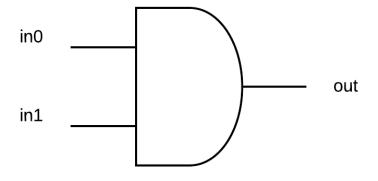

| in0 | in1 | out |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 0   |

| 1   | 0   | 0   |

| 1   | 1   | 1   |

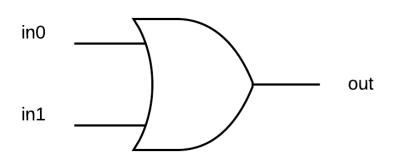

**Graphical Representation**

Truth Table

| in0 | in1 | out |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 1   |

| 1   | 0   | 1   |

| 1   | 1   | 1   |

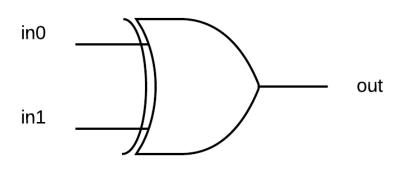

**Graphical Representation**

Truth Table

| in0 | in1 | out |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 1   |

| 1   | 0   | 1   |

| 1   | 1   | 0   |

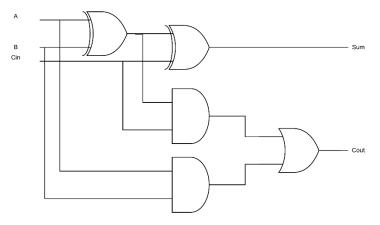

**Graphical Representation**

Truth Table

| Α | В | Cin | Sum | Cout |

|---|---|-----|-----|------|

| 0 | 0 | 0   | 0   | 0    |

| 0 | 0 | 1   | 1   | 0    |

| 0 | 1 | 0   | 1   | 0    |

| 0 | 1 | 1   | 0   | 1    |

| 1 | 0 | 0   | 1   | 0    |

| 1 | 0 | 1   | 0   | 1    |

| 1 | 1 | 0   | 0   | 1    |

| 1 | 1 | 1   | 1   | 1    |

Truth Table

Graphical Representation

UG479\_c1\_21\_032111

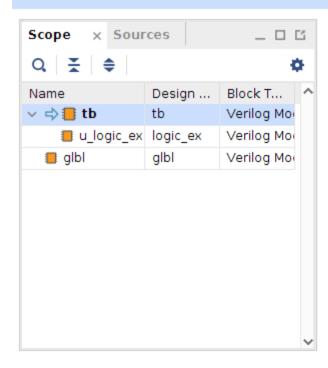

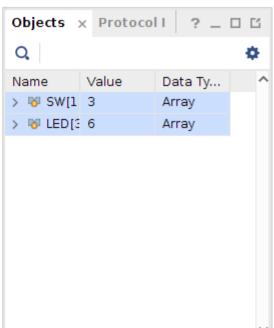

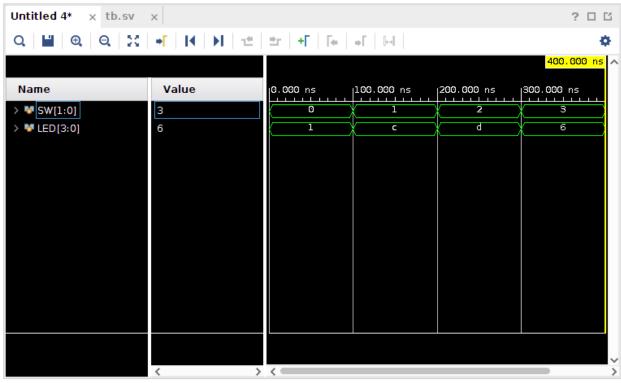

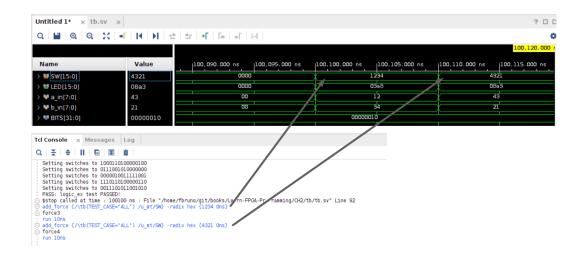

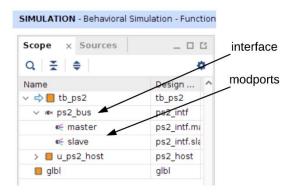

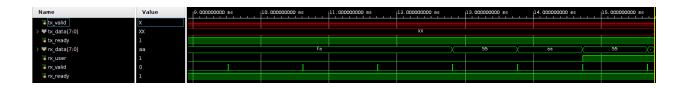

### SIMULATION - Behavioral Simulation - Functional - sim\_1 - tb

```

Tcl Console

x Messages

Log

Q X 🛊 🗎 🖫

# set curr_wave [current_wave_config]

# if { [string length $curr_wave] == 0 } {

if { [llength [get_objects]] > 0} {

add_wave /

#

set_property needs_save false [current_wave_config]

#

} else {

send msg id Add Wave-1 WARNING "No top level signals found. Simulator will start without a w

#

#

# }

# run 1000ns

Timescale of (tb) is lns/100ps.

Setting switches to 00

Setting switches to 01

Setting switches to 10

Setting switches to 11

PASS: logic_ex test PASSED!

$stop called at time : 400 ns : File "/home/fbruno/git/private/book/CH1/tb/tb.sv" Line 20

INFO: [USF-XSim-96] XSim completed. Design snapshot 'tb_behav' loaded.

INFO: [USF-XSim-97] XSim simulation ran for 1000ns

| launch_simulation: Time (s): cpu = 00:00:06; elapsed = 00:00:06. Memory (MB): peak = 8121.176; g

| current_wave_config {}

WARNING: [Wavedata 42-16] Error Unable to get wave configuration ''.

add wave {{/tb/SW}} {{/tb/LED}}}

```

Type a Tcl command here

# **Chapter 2: Combinational Logic**

| tilization |             |    | Post-Synt | hesis   Pos   | st-Implementation |

|------------|-------------|----|-----------|---------------|-------------------|

|            |             |    |           |               | Graph   Table     |

| Resource   | Utilization | Α  | vailable  | Utilization % | 6                 |

| LUT        |             | 61 | 63400     | )             | 0.10              |

| 10         |             | 32 | 210       | )             | 15.24             |

| <b>Utilization</b> Post-Synthesis |             |           | Post-Implementation  |

|-----------------------------------|-------------|-----------|----------------------|

|                                   |             |           | Graph   <b>Table</b> |

| Resource                          | Utilization | Available | Utilization %        |

| LUT                               | 134         | 63400     | 0.21                 |

| 10                                | 37          | 210       | 17.62                |

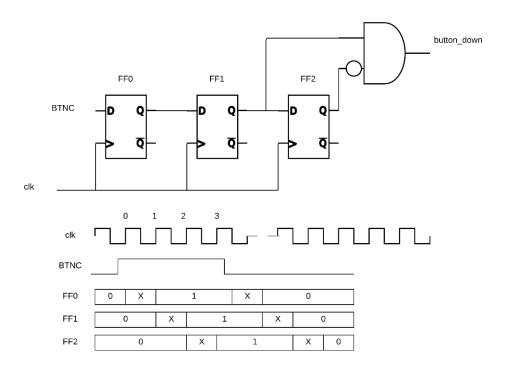

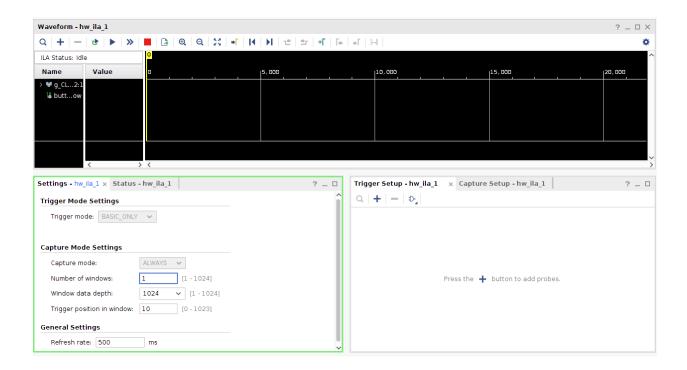

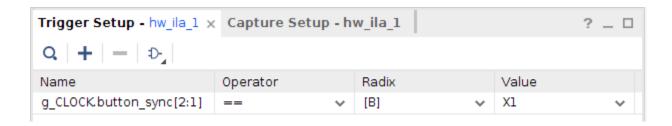

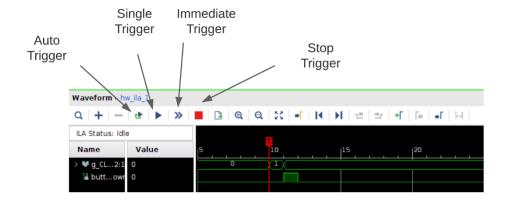

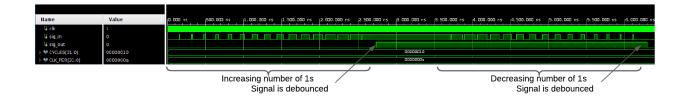

### **Chapter 3: Counting Button Presses**

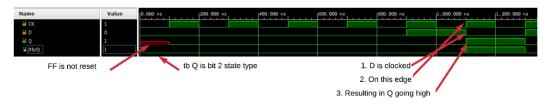

- - √ im sim\_1 (2 errors)

- [VRFC 10-3818] variable 'Q' is driven by invalid combination of procedural drivers [simple\_init\_ff.sv:6]

- (9) [XSIM 43-3322] Static elaboration of top level Verilog design unit(s) in library work failed.

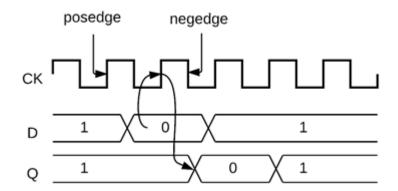

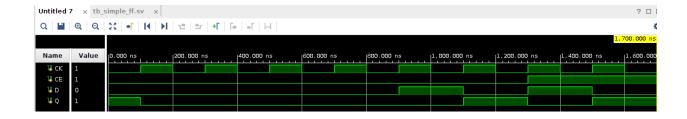

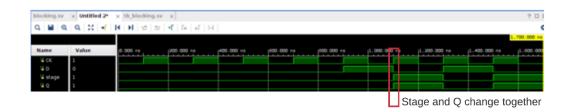

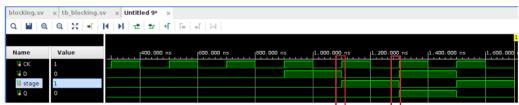

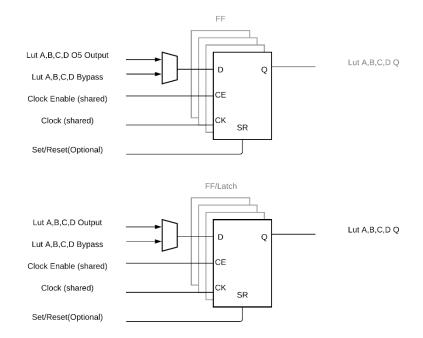

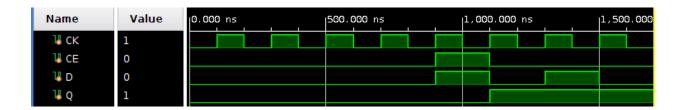

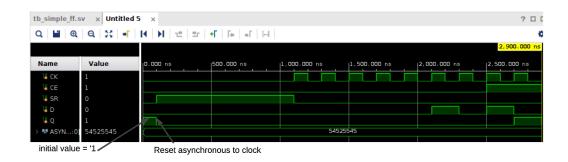

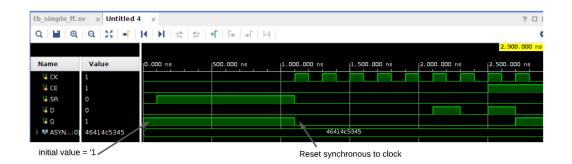

Every clock cycle, Q gets the previous value of stage and stage gets the previous value of D

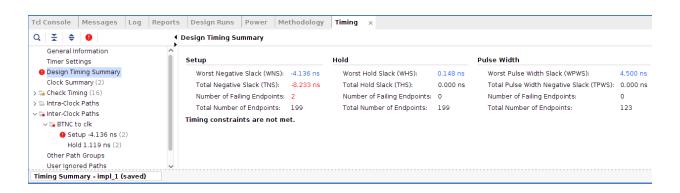

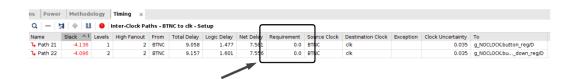

#### **Design Timing Summary**

| Setup                          |             | Hold                         |          | Pulse Width                              |          |

|--------------------------------|-------------|------------------------------|----------|------------------------------------------|----------|

| Worst Negative Slack (WNS):    | 6.498 ns    | Worst Hold Slack (WHS):      | 0.169 ns | Worst Pulse Width Slack (WPWS):          | 4.500 ns |

| Total Negative Slack (TNS):    | 0.000 ns    | Total Hold Slack (THS):      | 0.000 ns | Total Pulse Width Negative Slack (TPWS): | 0.000 ns |

| Number of Failing Endpoints:   | 0           | Number of Failing Endpoints: | 0        | Number of Failing Endpoints:             | 0        |

| Total Number of Endpoints:     | 168         | Total Number of Endpoints:   | 168      | Total Number of Endpoints:               | 125      |

| All user specified timing cons | traints are | e met.                       |          |                                          |          |

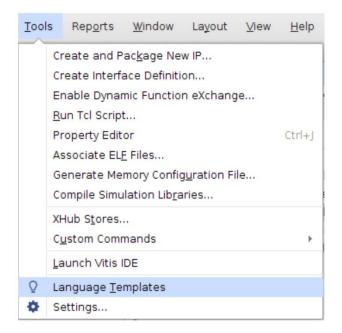

| <u>T</u> ool | s Rep <u>o</u> rts                                                                                                                                     | <u>W</u> indow                                                                 | Layout                                | ⊻iew | <u>H</u> elp       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------|------|--------------------|

|              | Eloorplanning  J/O Planning  Timing  Power Constr                                                                                                      |                                                                                | or.                                   |      | 1                  |

| Ħ            | Schematic<br>Show Connect<br>Show Hierarch                                                                                                             | tivity<br><b>Y</b>                                                             |                                       |      | F4<br>Ctrl+'<br>F6 |

|              | Edit Device Pr<br>Create and Pr<br>Create Interfa<br>Enable Dynan<br>Bun Tcl Script<br>Property Edito<br>Associate ELE<br>Generate Mer<br>Compile Simu | ackage New<br>ace Definition<br>nic Function<br><br>or<br>Files<br>mory Config | on<br>n eXchang<br><u>u</u> ration Fi |      | Ctrl+J             |

| *            | Set Up Debug                                                                                                                                           | J                                                                              |                                       |      |                    |

|              | XHub Stores<br>Custom Comm<br>Launch Vitis II                                                                                                          | nands                                                                          |                                       |      |                    |

| <b>Ω</b>     | Language <u>T</u> er<br>Settings                                                                                                                       | mplates                                                                        |                                       |      |                    |

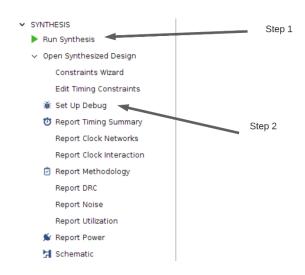

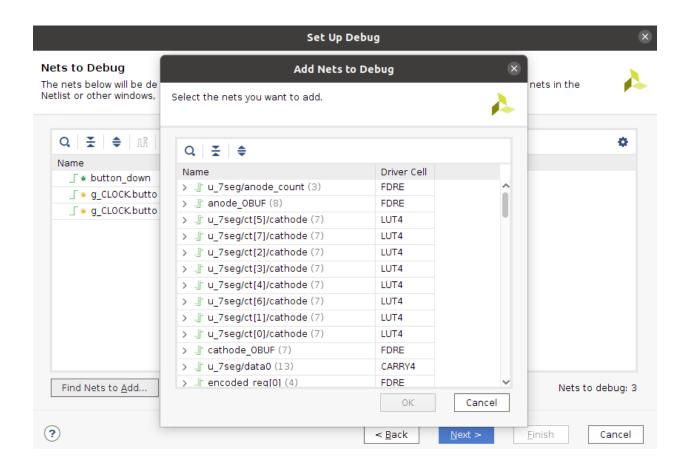

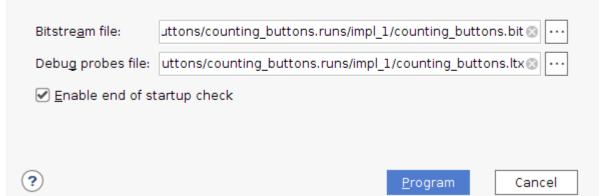

#### Program Device

Select a bitstream programming file and download it to your hardware device. You can optionally select a debug probes file that corresponds to the debug cores contained in the bitstream programming file.

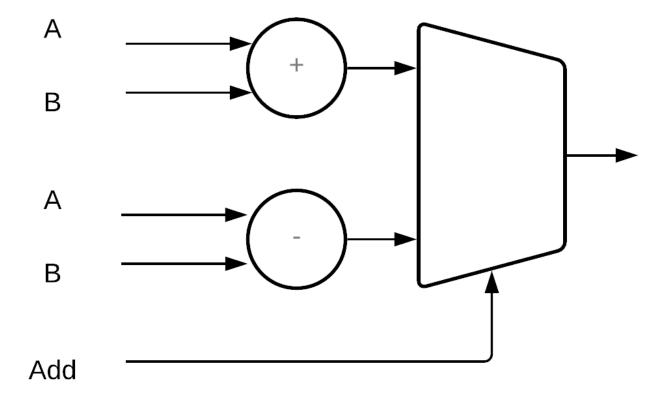

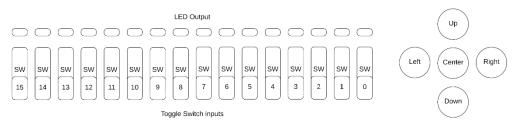

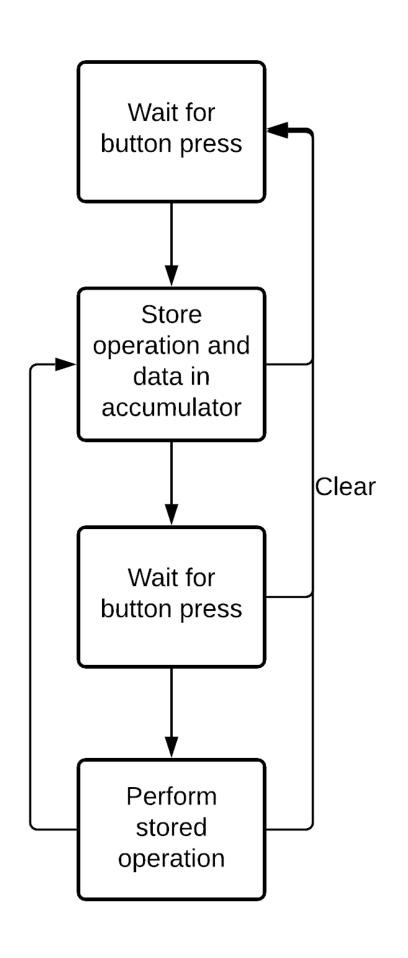

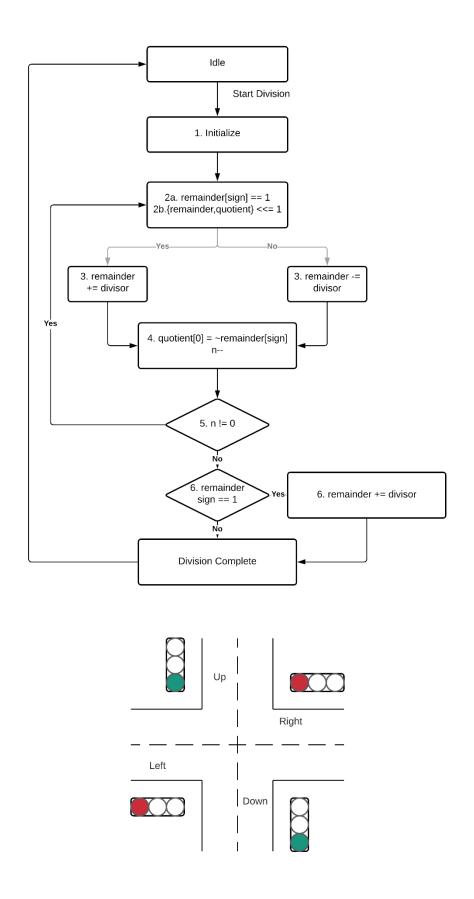

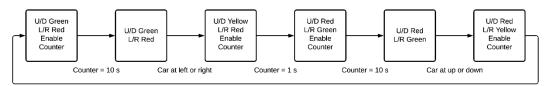

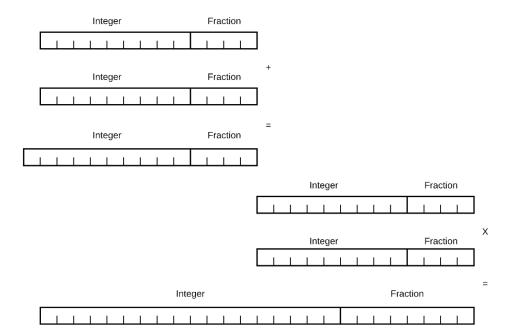

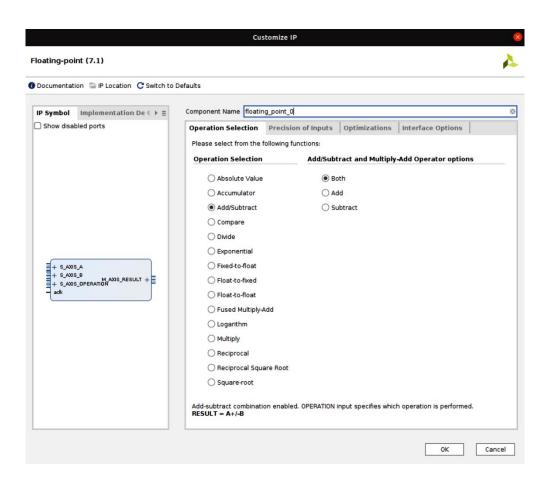

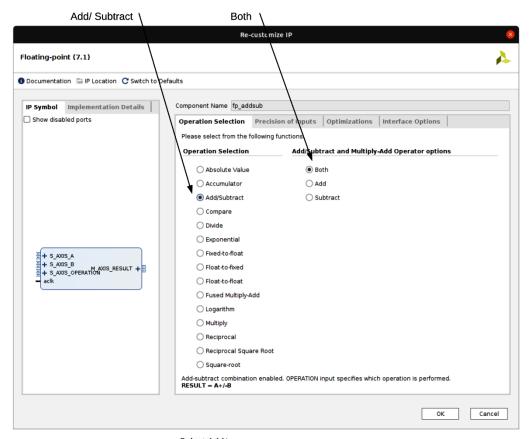

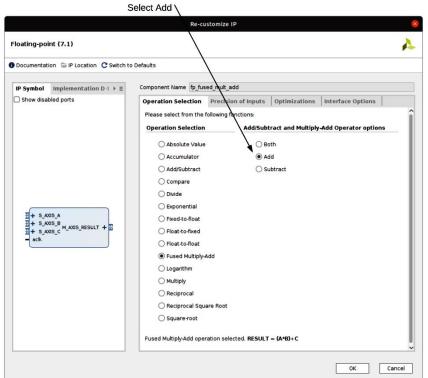

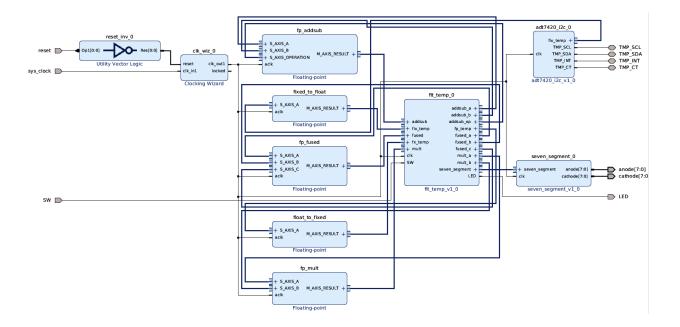

## **Chapter 4: Let's Build a Calculator**

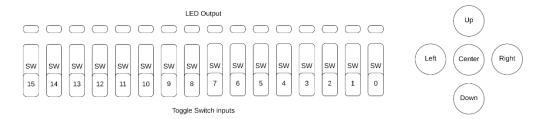

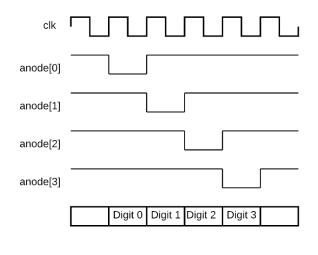

Push Buttons

Counter = 1 s

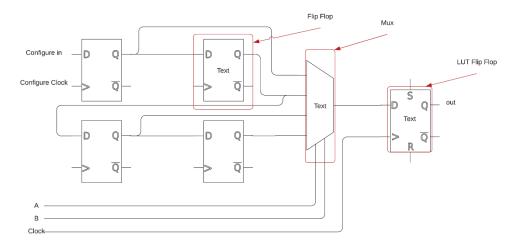

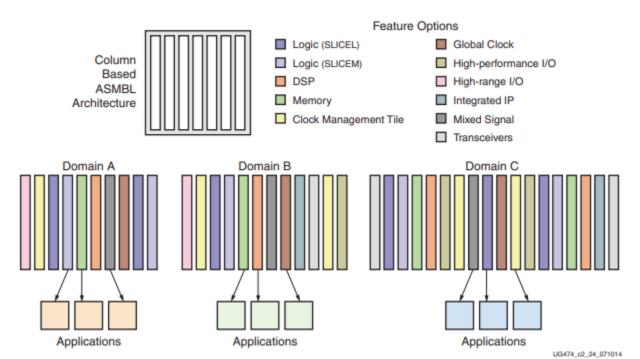

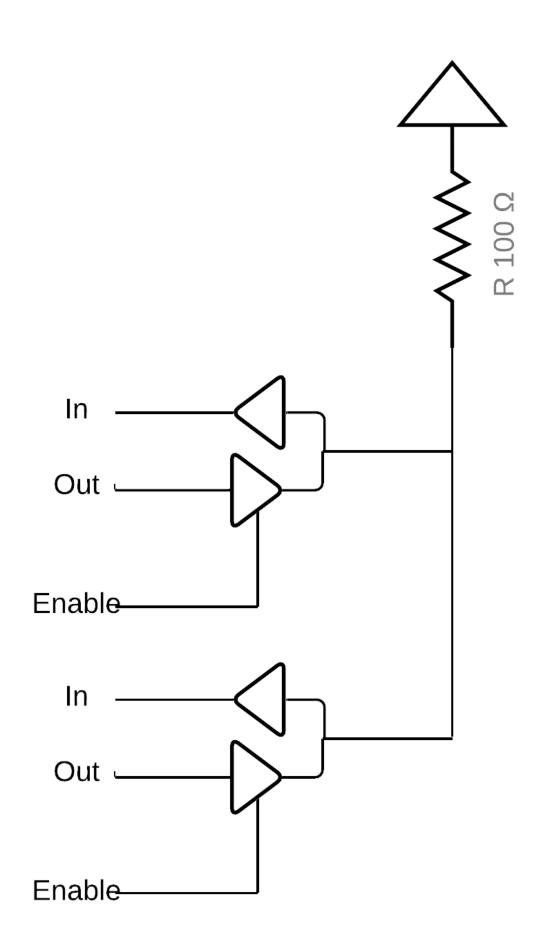

**Chapter 5: FPGA Resources and How to Use Them**

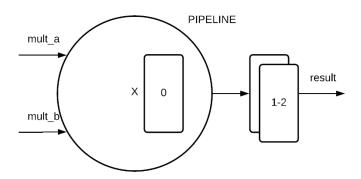

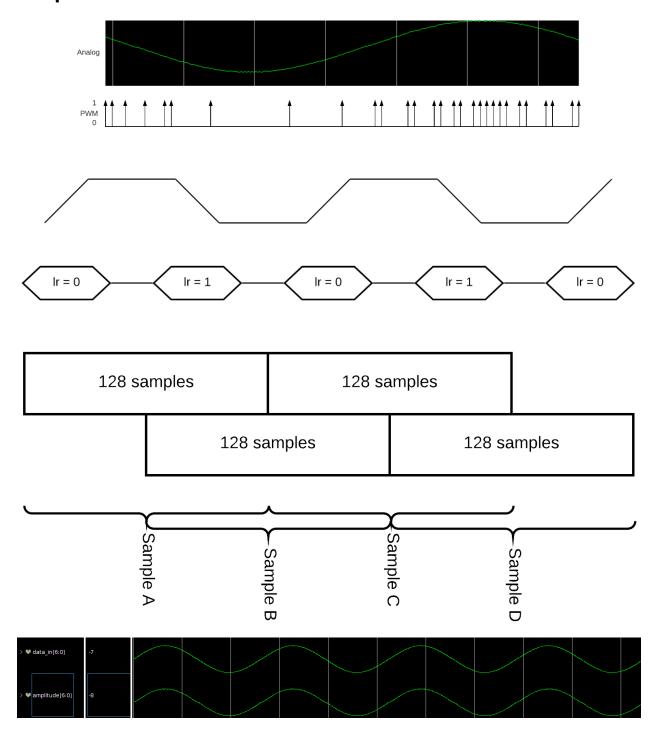

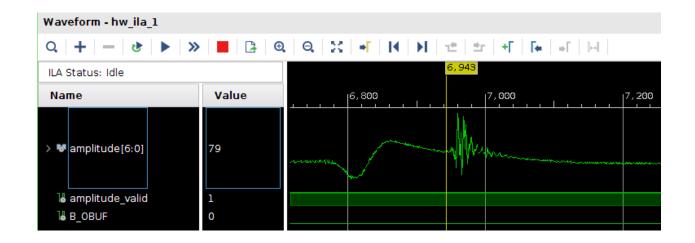

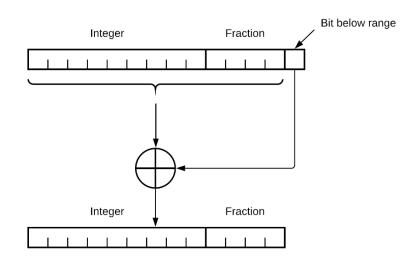

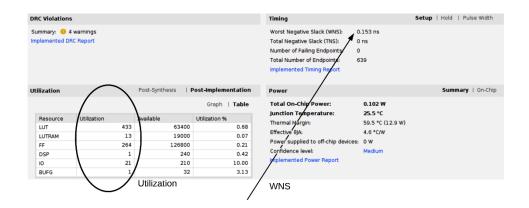

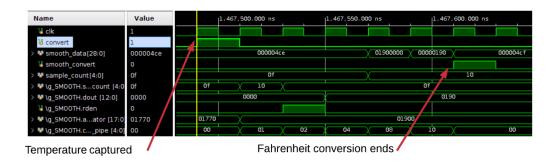

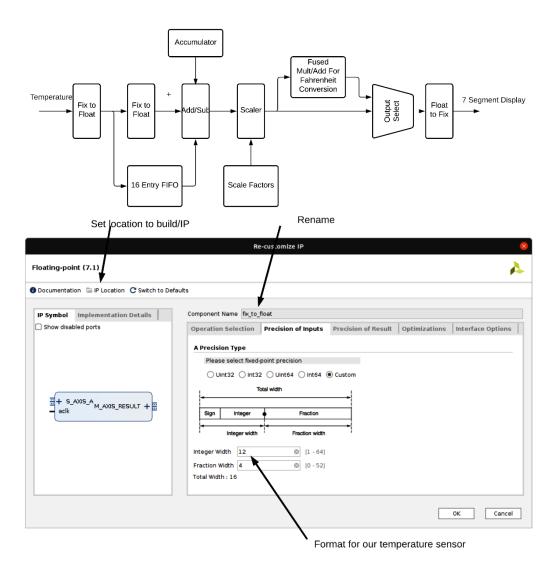

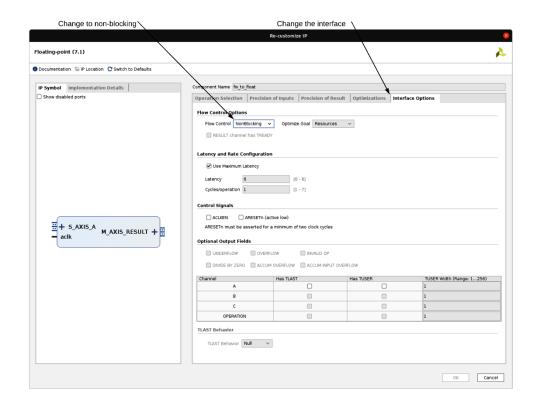

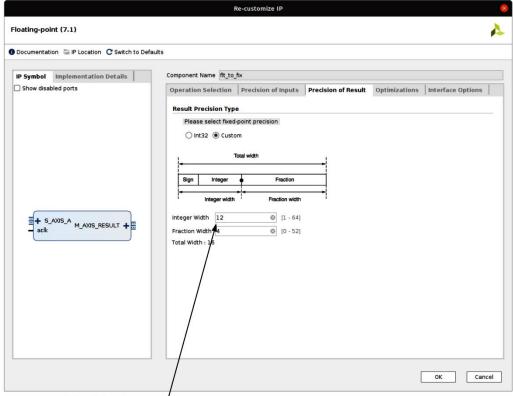

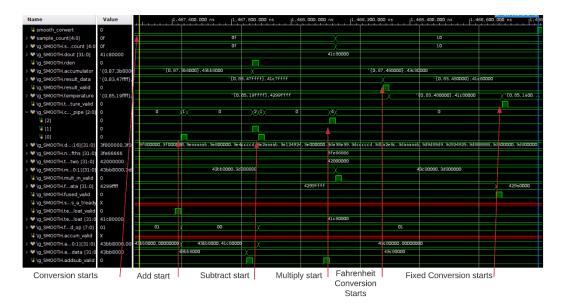

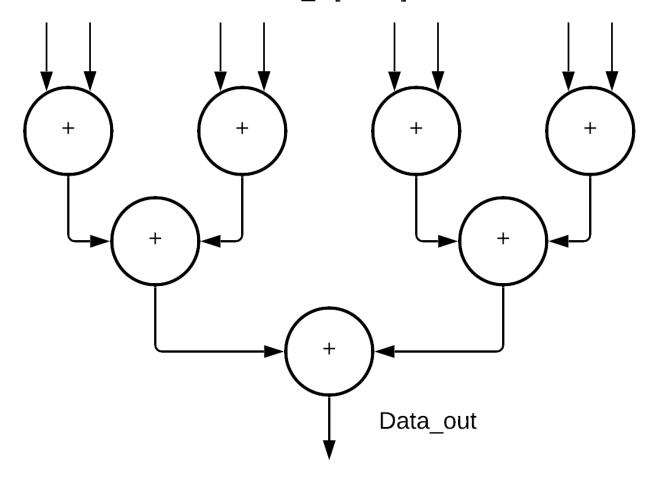

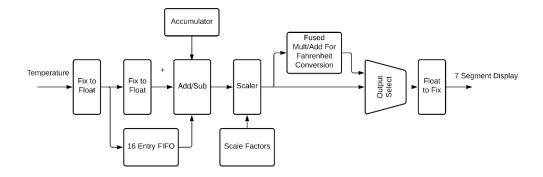

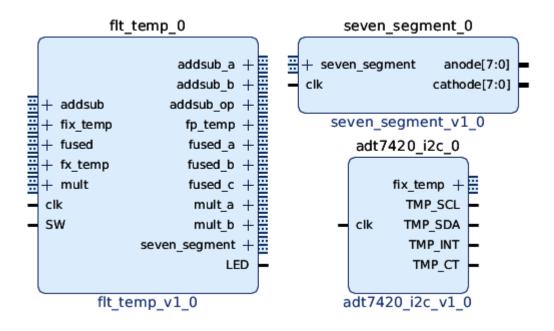

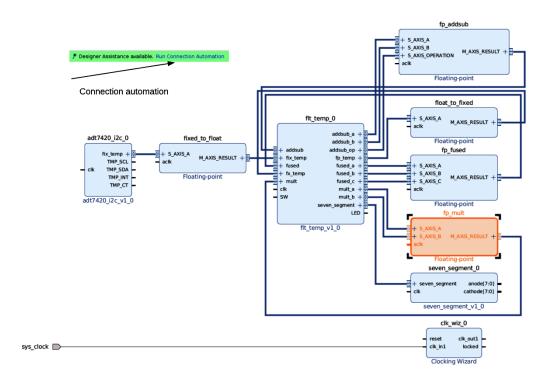

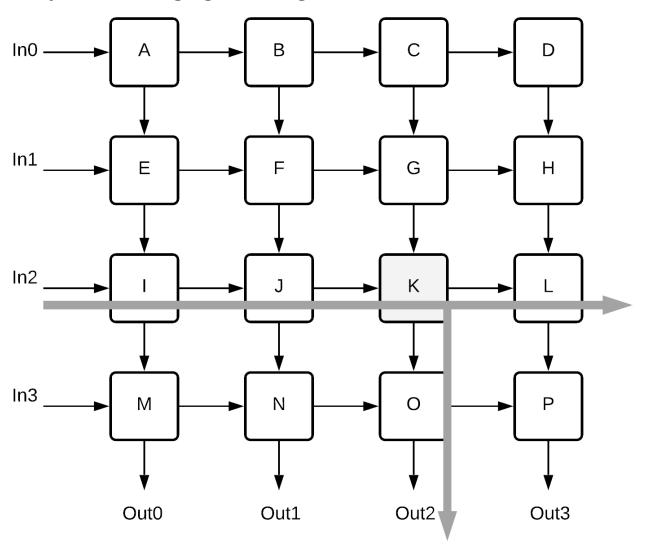

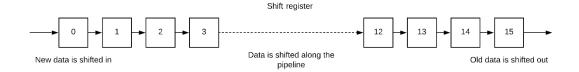

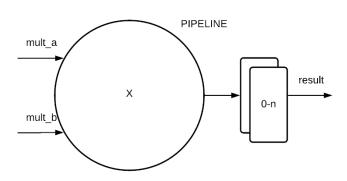

### Chapter 6: Math, Parallelism, and Pipelined Design

$$T_{Fahrenheit} = \left(T_{Celsius} \ x \frac{9}{5}\right) + 32$$

| sign |  |   |   | exponent |   |  |               |   |   |                   |   |  |   |   | fraction |   |   |   |   |   |   |   |   |   |   |   |  |   |  |                   |  |

|------|--|---|---|----------|---|--|---------------|---|---|-------------------|---|--|---|---|----------|---|---|---|---|---|---|---|---|---|---|---|--|---|--|-------------------|--|

|      |  | ı | ī | ī        | ı |  | $\overline{}$ | ī | Γ | $\overline{\Box}$ | ī |  | Ι | ī | ī        | ı | ı | Ι | ı | ı | ı | ī | 1 | ı | ı | 1 |  | ī |  | $\overline{\Box}$ |  |

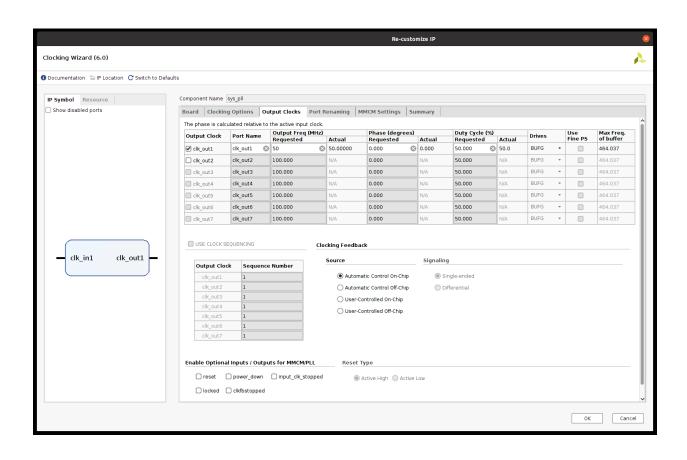

Select 8.4 as the output

Data\_in[255:0]

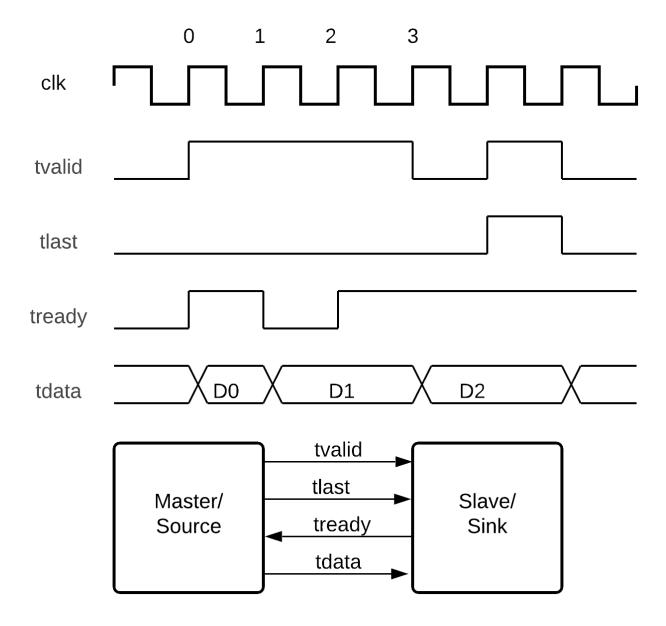

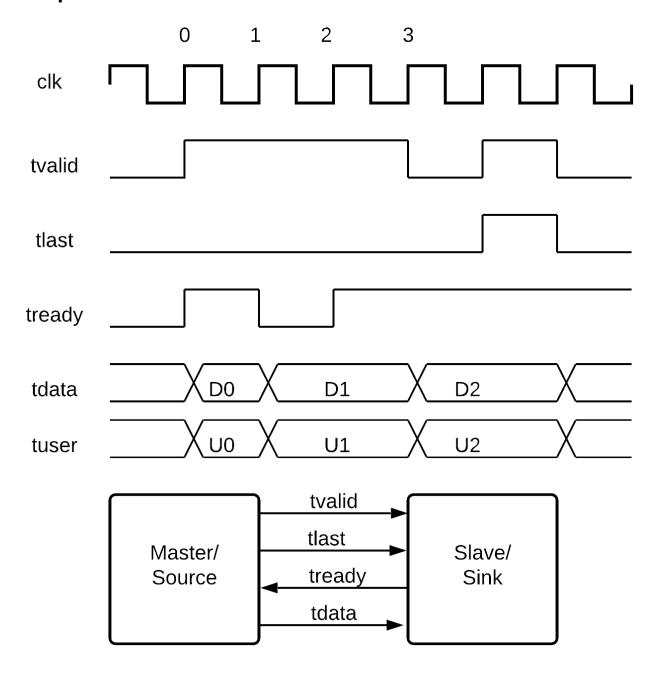

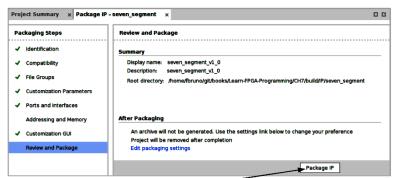

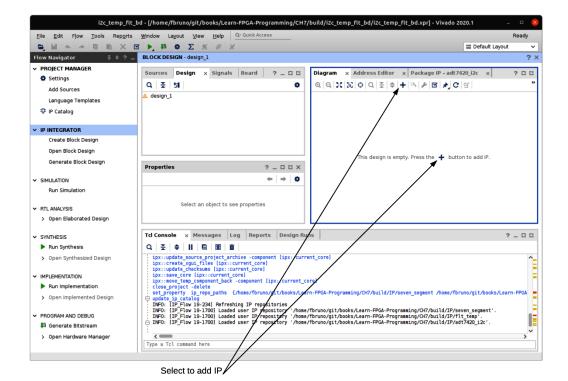

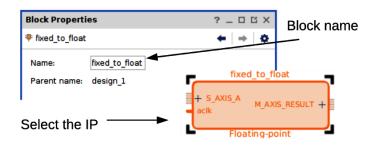

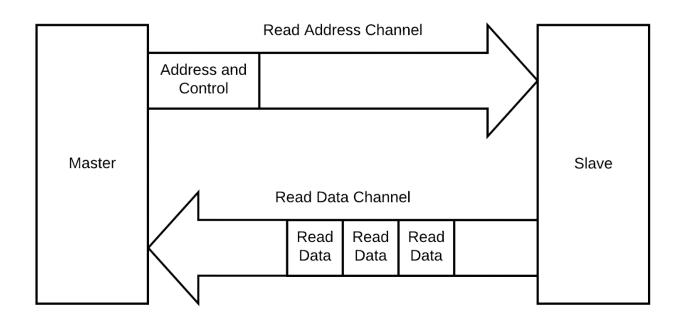

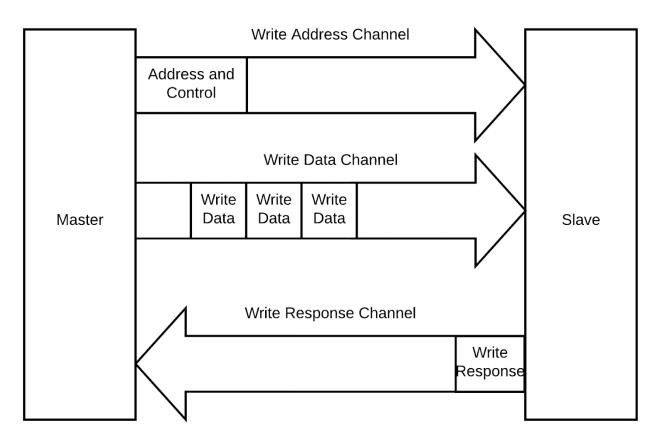

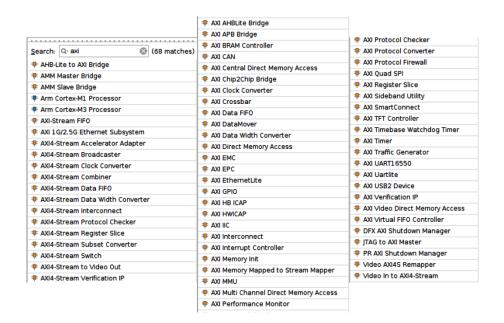

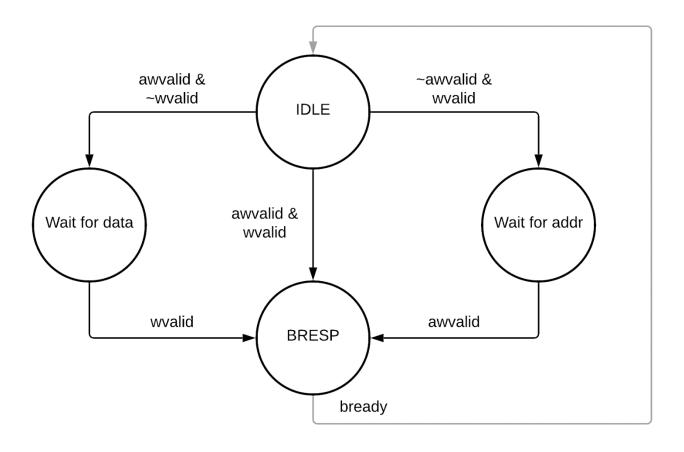

## **Chapter 7: Introduction to AXI**

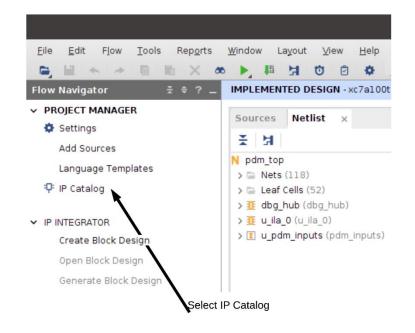

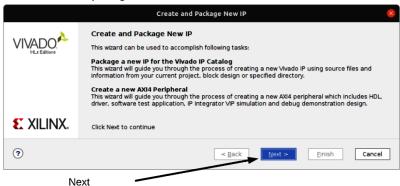

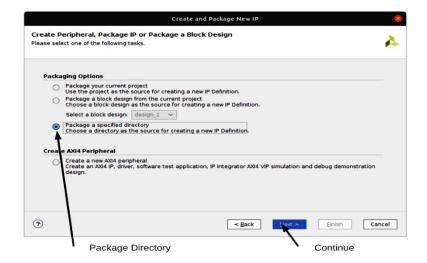

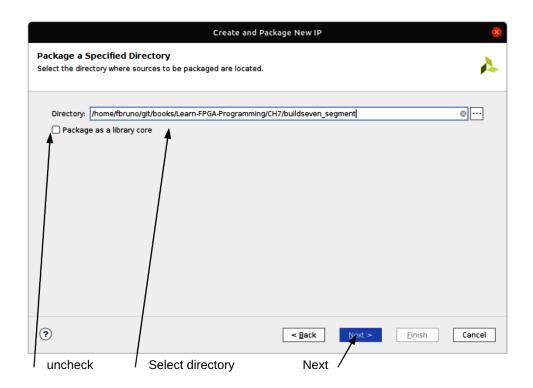

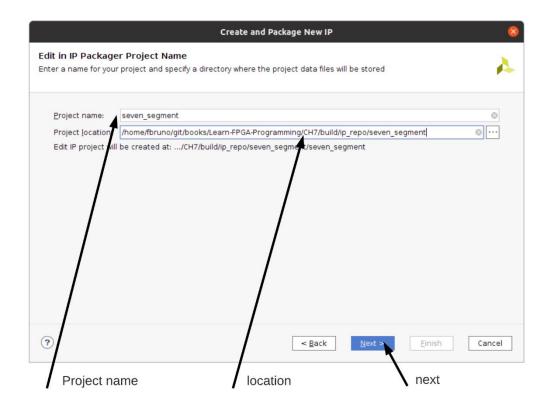

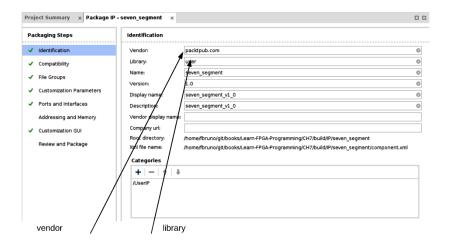

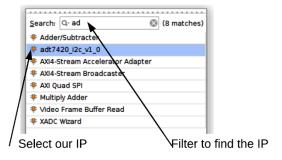

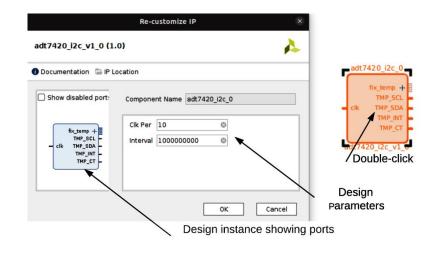

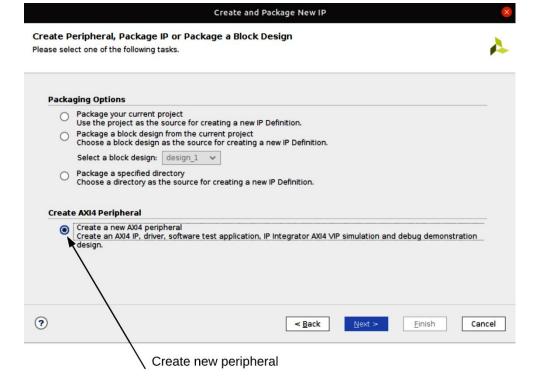

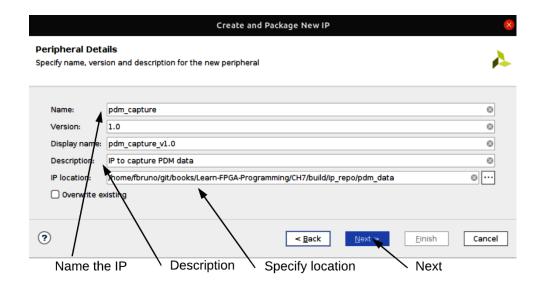

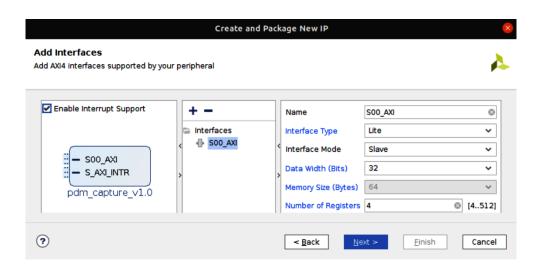

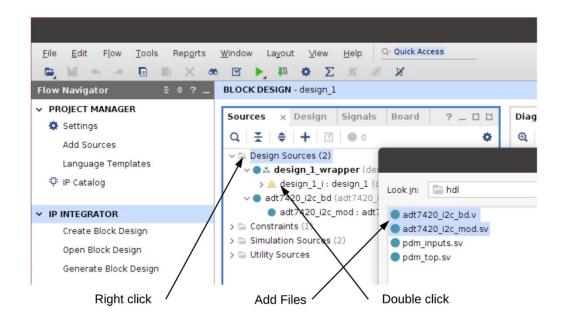

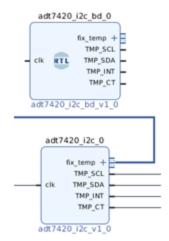

### tools->Create and package IP

#### **Ports and Interfaces**

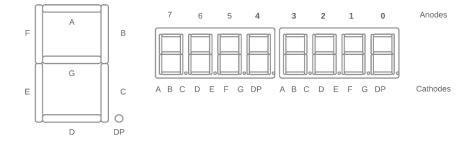

| Name                    | Interface<br>Mode | Enablement<br>Dependency | Direction | Driver<br>Value | Size<br>Left | Size<br>Right | Size Left Dependency | Size Right<br>Dependency | Type<br>Name |

|-------------------------|-------------------|--------------------------|-----------|-----------------|--------------|---------------|----------------------|--------------------------|--------------|

| √                       | slave             |                          |           |                 |              |               |                      |                          |              |

| seven_segment_tdata     |                   |                          | in        | 0               | 31           | 0             | ((NUM_SEGMENTS * 4)  |                          | wire         |

| seven_segment_tuser     |                   |                          | in        | 0               | 7            | 0             | (NUM_SEGMENTS - 1)   |                          | wire         |

| seven_segment_tvalid    |                   |                          | in        |                 |              |               |                      |                          | wire         |

| Clock and Reset Signals |                   |                          |           |                 |              |               |                      |                          |              |

| >                       | slave             |                          |           |                 |              |               |                      |                          |              |

| anode                   |                   |                          | out       |                 | 7            | 0             | (NUM_SEGMENTS - 1)   |                          | logic        |

| cathode                 |                   |                          | out       |                 | 7            | 0             |                      |                          | logic        |

Package IP

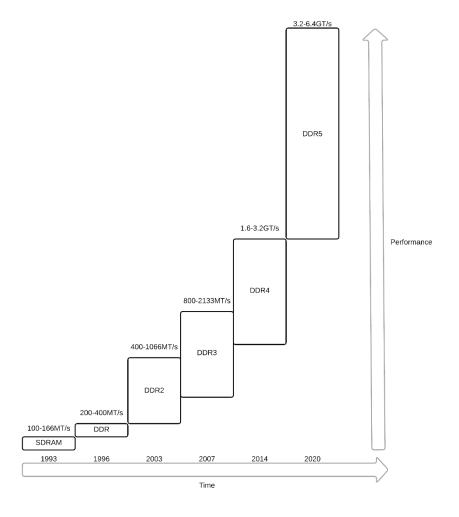

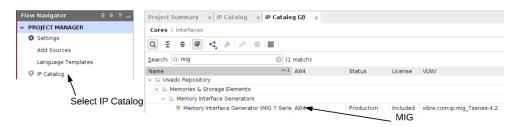

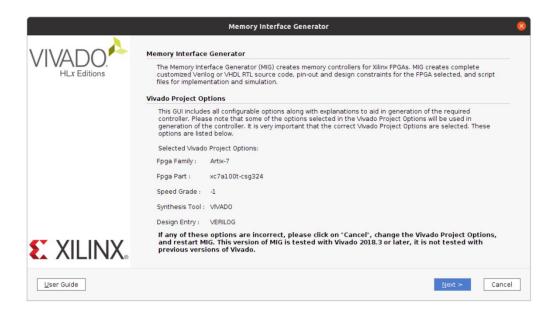

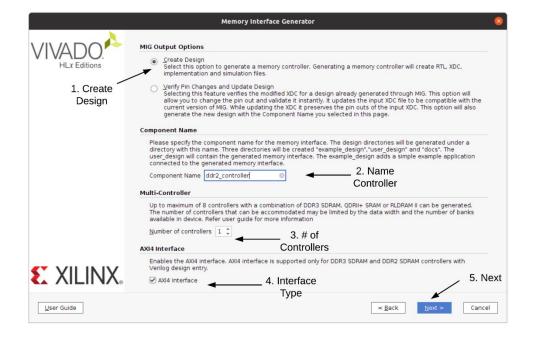

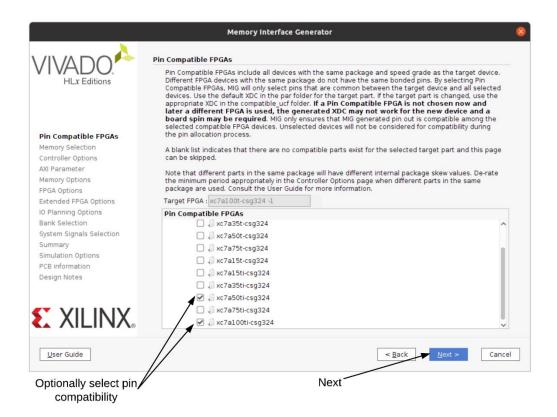

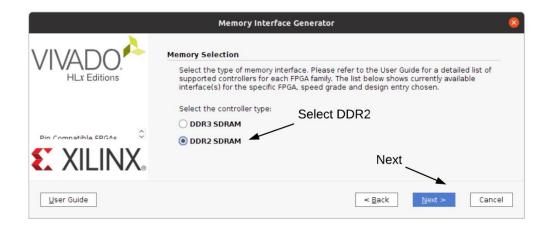

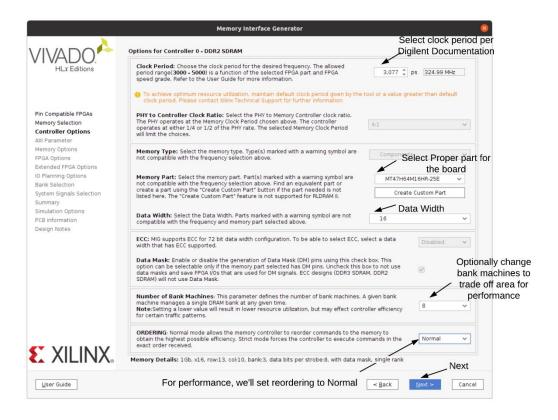

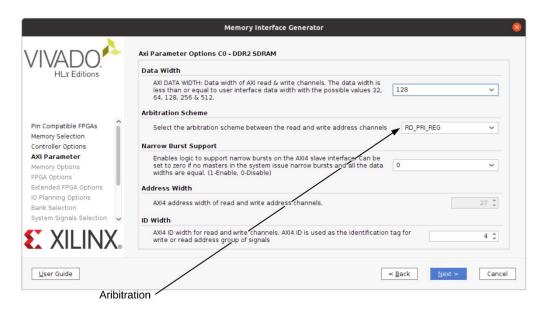

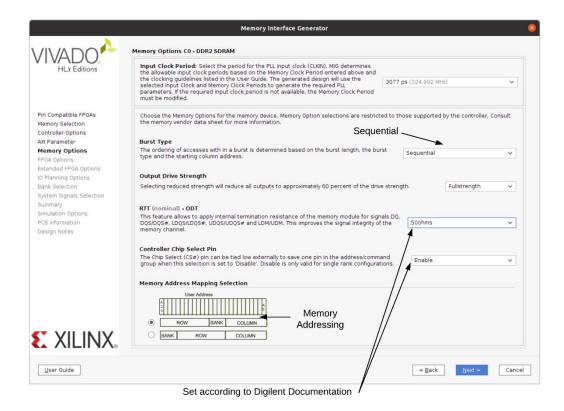

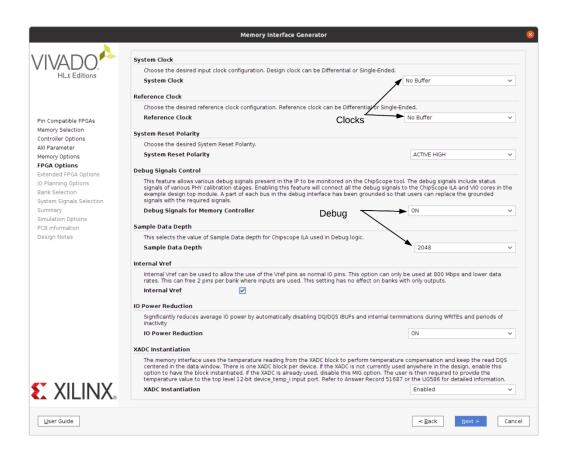

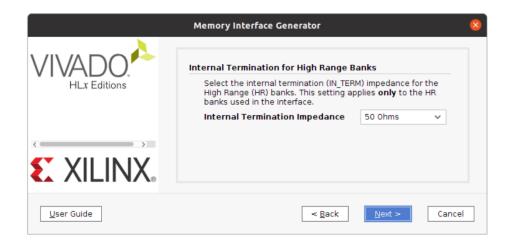

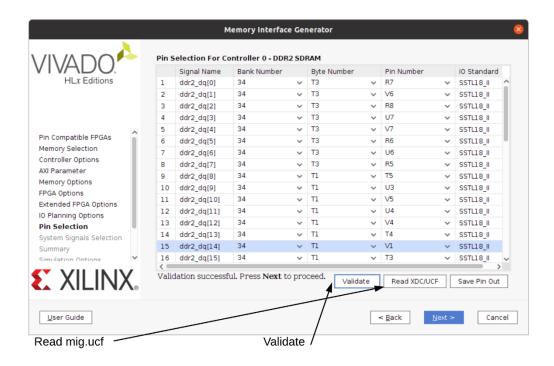

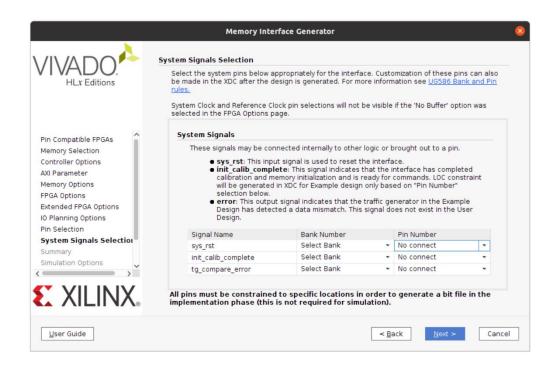

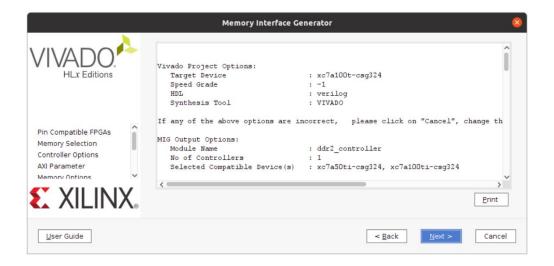

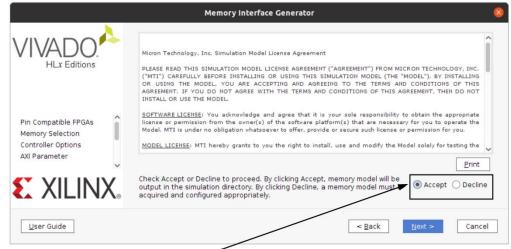

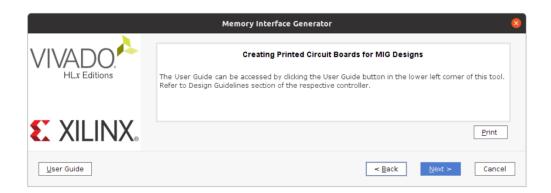

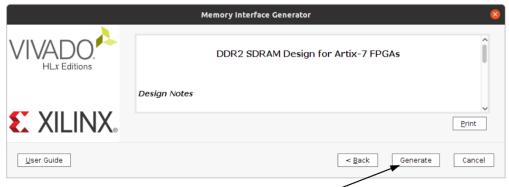

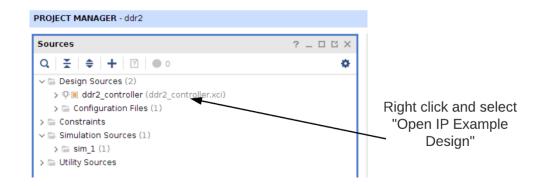

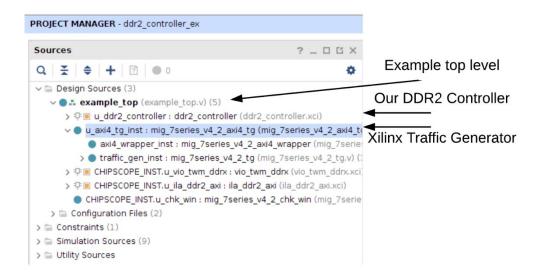

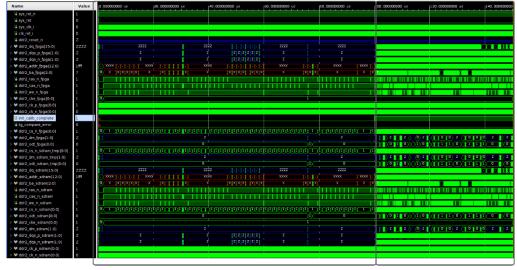

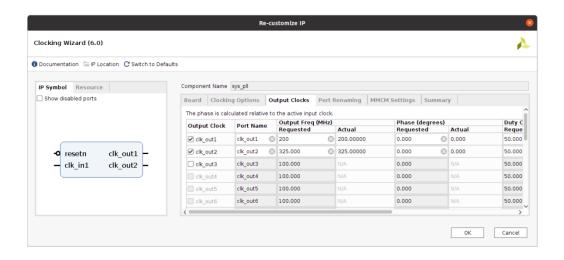

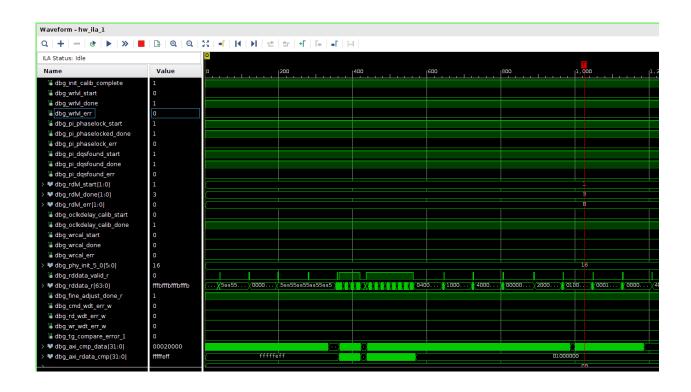

# Chapter 8: Lots of Data? MIG and DDR2

Accept for memory model-

Generate Memory Controller

Device Initialization and Calibration

Traffic Generator Test

```

548 🖯

549

// Reporting the test case status

// Status reporting logic exists both in simulation test bench (sim_tb_top)

// and sim.do file for ModelSim. Any update in simulation run time or time out

// in this file need to be updated in sim.do file as well.

550

551

552

553 ⊖

554

initial

555

begin : Logging

556

fork

557

begin : calibration_done

558

00000

wait (init_calib_complete);

559

$display("Calibration Done");

560

#50000000.0;

561

if (!tg_compare_error) begin

562

$display("TEST PASSED");

563

564

else begin

$display("TEST FAILED: DATA ERROR");

565

0

566

end

0

567

disable calib_not_done;

$finish;

568

\bigcirc

569

end

```

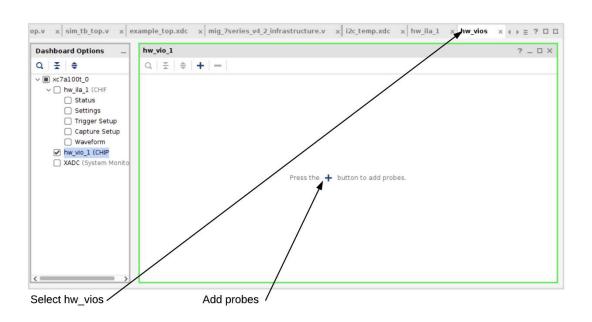

| hw_vio_1                                 |                  |          |           |           | ? _ 🗆 X                               |

|------------------------------------------|------------------|----------|-----------|-----------|---------------------------------------|

| Q   🛨   💠   +   🗕                        |                  |          |           |           |                                       |

| Name                                     | Value            | Activity | Direction | VIO       |                                       |

| l₀ vio_modify_enable                     | [B] 0 ————       |          | —Output — | -hw_vio_1 |                                       |

| ୗ₄ vio_tg_rst                            | [B] 0 •          |          | Output    | hw_vio_1  |                                       |

| > 1 vio_tg_simple_data_sel[1:0]          | [H] 0 ×          |          | Output    | hw_vio_1  |                                       |

| Ղ₄ wdt_en_w                              | [B] 0 *          |          | Output    | hw_vio_1  |                                       |

| ו <sub>∞</sub> win_active                | [B] 0            |          | Input     | hw_vio_1  |                                       |

| > 1 win_byte_select[6:0]                 | [H] 00           |          | Input     | hw_vio_1  |                                       |

| > 1 win current bit[6:0]                 | [H] 00           |          | Input     | hw_vio_1  |                                       |

| > 1 win_current_byte[3:0]                | [H] 0            |          | Input     | hw_vio_1  |                                       |

| וֹ₀ win_start_1                          | [B] 0            |          | Input     | hw_vio_1  |                                       |

| > 1 vio_addr_mode_value[2:0]             | [H] 2            |          | Output    | hw_vio_1  |                                       |

| l₄ vio_dbg_pi_f_inc                      | [B] 0 *          |          | Output    | hw_vio_1  | · · · · · · · · · · · · · · · · · · · |

| l₀ vio_dbg_po_f_dec                      | [B] 0 ~          |          | Output    | hw_vio_1  |                                       |

| l₀ vio_dbg_po_f_stg23_sel                | [B] 0 *          |          | Output    | hw_vio_1  |                                       |

| > 1 vio_fixed_instr_value[2:0]           | [H] 0 •          |          | Output    | hw_vio_1  |                                       |

| > % po_win_right_ram_out[8:0]            | [H] 000          |          | Input     | hw_vio_1  |                                       |

| l <sub>o</sub> dbg_mem_pattern_init_done | [B] 0            |          | Input     | hw_vio_1  |                                       |

| > 1 dbg_pi_counter_read_val[5:0]         | [H] 24           |          | Input     | hw_vio_1  |                                       |

| by the dbg_po_counter_read_val[8:0]      | [H] 097          |          | Input     | hw_vio_1  |                                       |

| l <sub>o</sub> dbg_tg_compare_error      | [B] 0            |          | Input     | hw_vio_1  |                                       |

| b dbg_tg_wr_data_counts[47:0]            | [H] 0000_0000_00 |          | Input     | hw_vio_1  |                                       |

| > 1 dbg_win_chk[164:0]                   | [H] 00 0000 0000 |          | Input     | hw_vio_1  |                                       |

| l <sub>a</sub> vio_pause_traffic         | [B] 0 *          |          | Output    | hw_vio_1  |                                       |

| > 1 vio_sel_mux_rdd[3:0]                 | [H] 0 ~          |          | Output    | hw_vio_1  |                                       |

| la vio_win_byte_select_dec               | [B] 0 ·          |          | Output    | hw_vio_1  |                                       |

| l <sub>α</sub> vio_win_byte_select_inc   | [B] 0 *          |          | Output    | hw_vio_1  |                                       |

| l₄ win_sel_pi_pon                        | [B] 0 *          |          | Output    | hw_vio_1  |                                       |

| l₄ win_start                             | [B] 0 *          |          | Output    | hw_vio_1  |                                       |

| > % pi_win_left_ram_out[5:0]             | [H] 00           |          | Input     | hw_vio_1  |                                       |

| l dbg_clear_error                        | [B] 0 •          |          | Output    | hw_vio_1  |                                       |

| > 1 dbg_bit[8:0]                         | [H] 000 ·        |          | Output    | hw_vio_1  |                                       |

| > 1 dbg_dqs[4:0]                         | [H] 00 ·         |          | Output    | hw_vio_1  |                                       |

| la vio_dbg_po_f_inc                      | [B] 0 *          |          | Output    | hw_vio_1  |                                       |

| > % vio_fixed_bl_value[9:0]              | [H] 000 ·        |          | Output    | hw_vio_1  |                                       |

| > 1 vio_bl_mode_value[1:0]               | [H] 2            |          | Output    | hw_vio_1  |                                       |

| l vio_data_mask_gen                      | [B] 0 •          |          | Output    | hw_vio_1  |                                       |

| l vio_dbg_sel_po_incdec                  | [B] 0 *          |          | Output    | hw_vio_1  |                                       |

| > 1 vio_instr_mode_value[3:0]            | [H] 0 •          |          | Output    | hw_vio_1  |                                       |

|                                          | [H] 7            |          | Output    | hw_vio_1  |                                       |

| la vio_dbg_sel_pi_incdec                 | [B] 0 *          |          | Output    | hw_vio_1  |                                       |

| la vio_dbg_pi_f_dec                      | [B] 0 *          |          | Output    | hw_vio_1  |                                       |

| > % pi_win_right_ram_out[5:0]            | [H] 00           |          | Input     | hw_vio_1  |                                       |

| > % po_win_left_ram_out[8:0]             | [H] 000          |          | Input     | hw_vio_1  |                                       |

| bo_wii_leit_laiii_out[0:0]               | [H] 0000_0000_00 |          | Input     | hw_vio_1  |                                       |

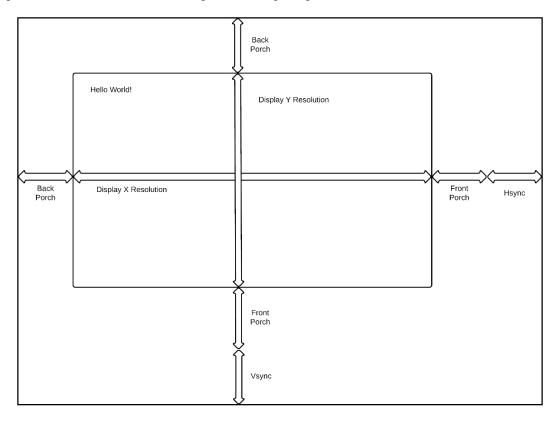

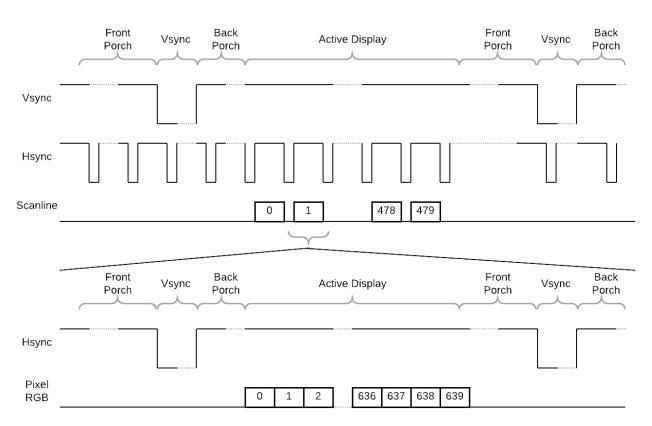

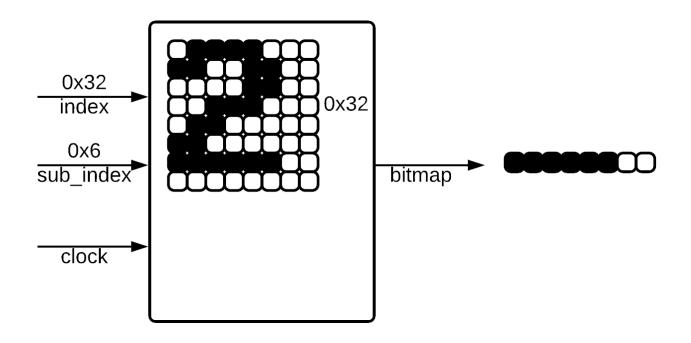

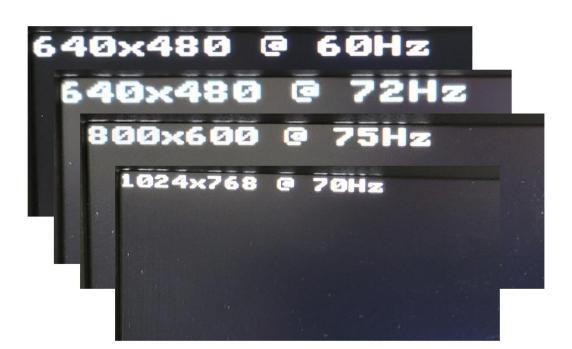

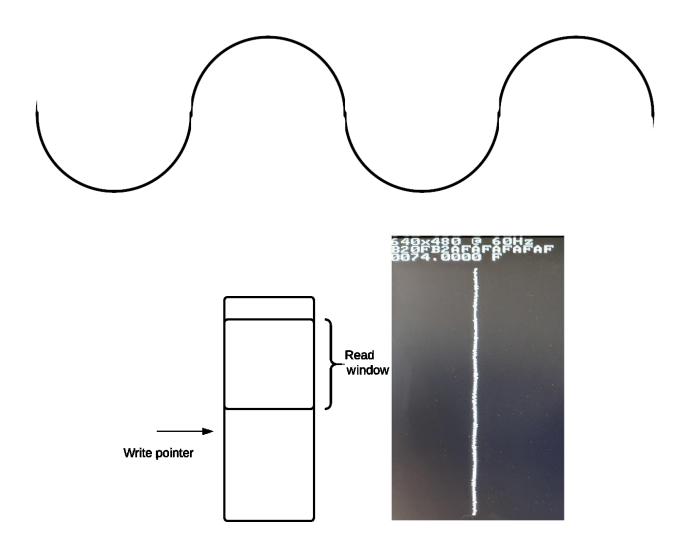

Chapter 9: A Better Way to Display – VGA

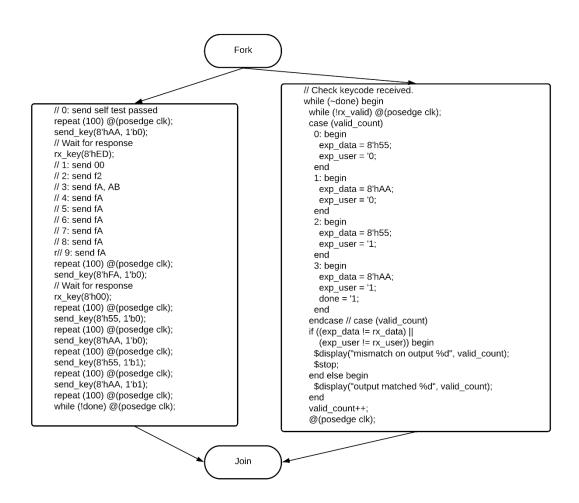

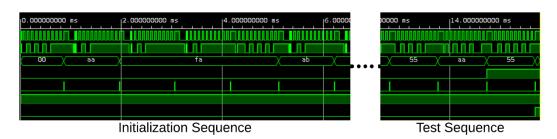

**Chapter 10: Bringing It All Together**

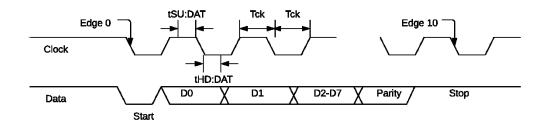

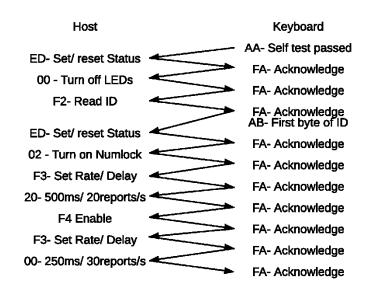

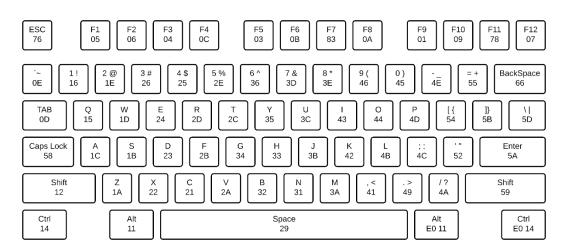

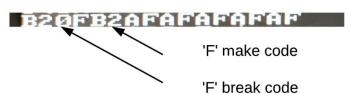

## PS/2 Scancodes

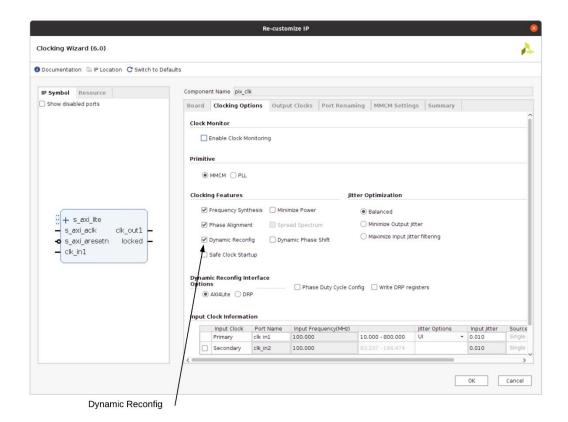

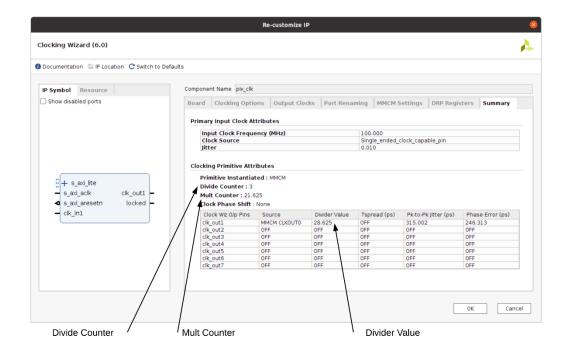

## **Chapter 11: Advanced Topics**

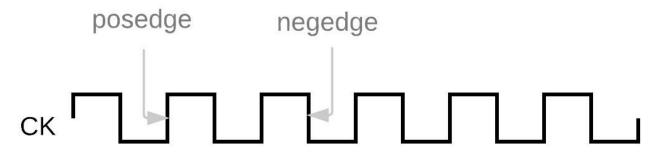

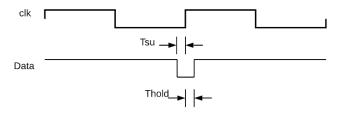

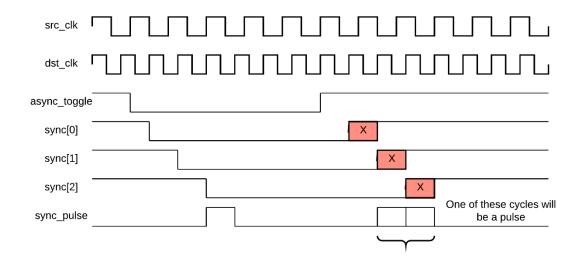

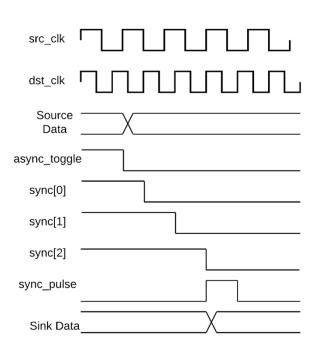

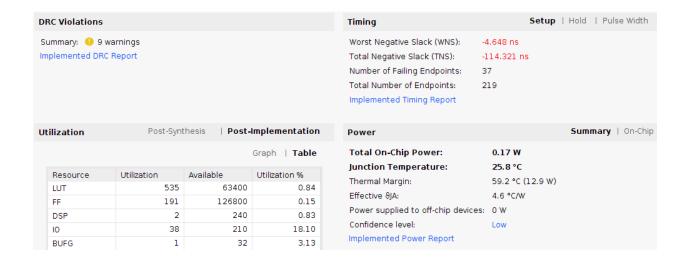

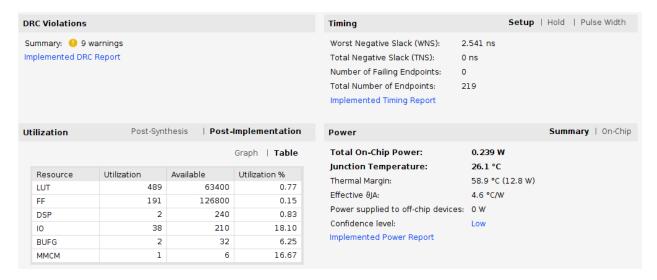

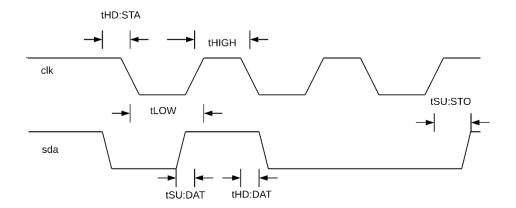

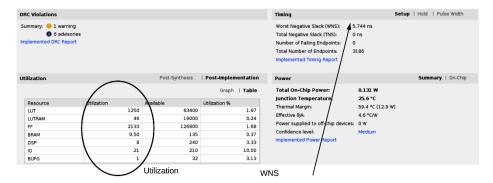

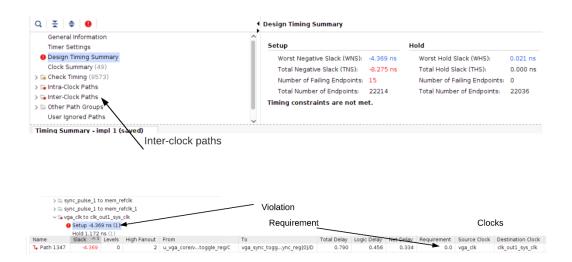

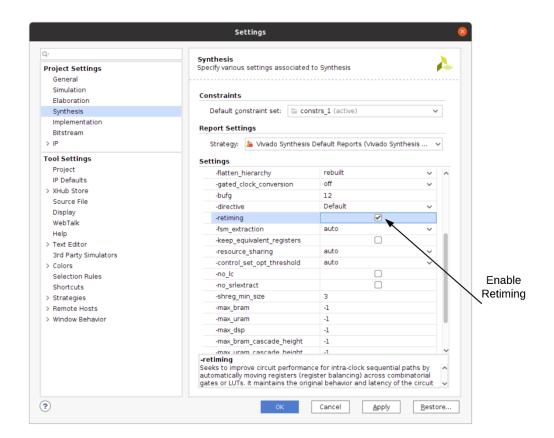

Timing

Setup | Hold | Pulse Width

Worst Negative Slack (WNS): -2.454 ns

Total Negative Slack (TNS): -257.8 ns

Number of Failing Endpoints: 125

Total Number of Endpoints: 535

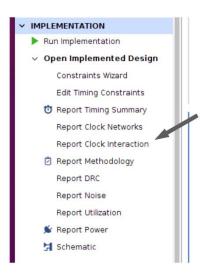

Implemented Timing Report

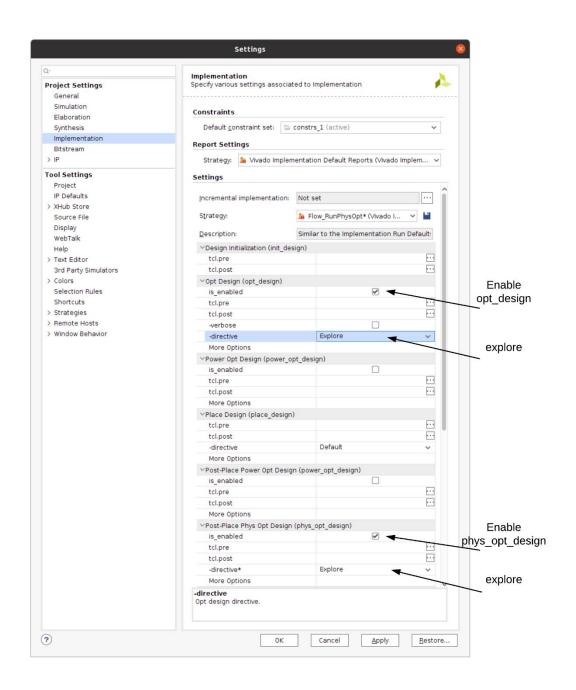

Timing Setup | Hold | Pulse Width

Worst Negative Slack (WNS): -1.139 ns

Total Negative Slack (TNS): -101.029 ns

Number of Failing Endpoints: 97

Total Number of Endpoints: 631

Implemented Timing Report

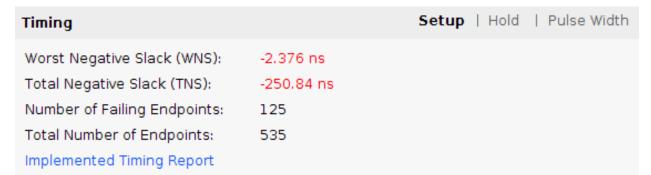

Timing Setup | Hold | Pulse Width

Worst Negative Slack (WNS): 0.444 ns

Total Negative Slack (TNS): 0 ns

Number of Failing Endpoints: 0

Total Number of Endpoints: 617

Implemented Timing Report